実現したいこと

今回、こちらのサイトを参照して、4ビットカウンタをXILINX社のPYNQ-Z1を使って実装を試みています。

発生している問題

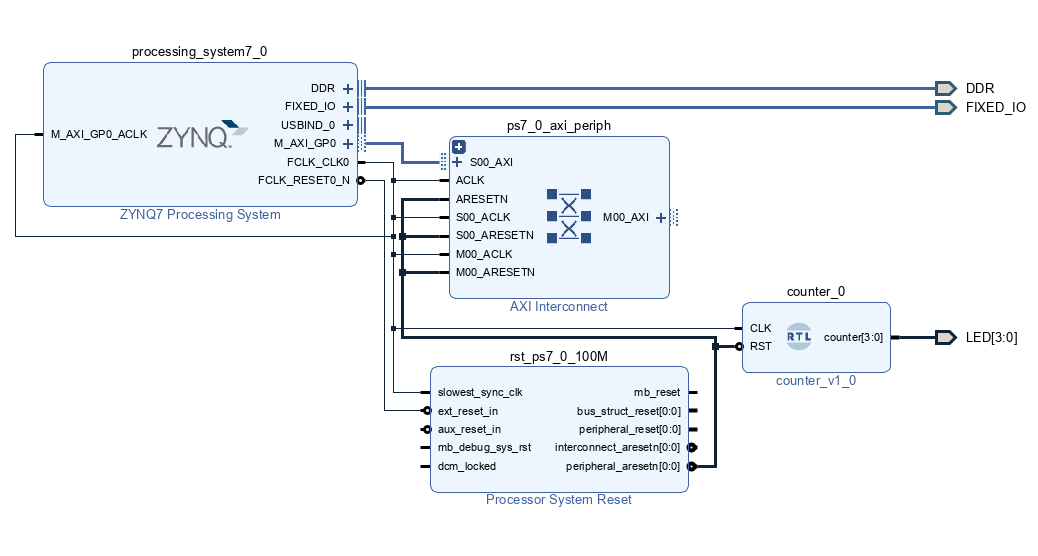

実際に、IPインテグレーターによるシステム構築を行い、ボード上で実装してみました。

初期状態で4つのLEDが光っていましたが、Jupyter notebookで実行したところすべてのLEDが消えてしまいました。

該当のソースコード

4ビットカウンタ回路のプログラム

Verilig

1module counter ( 2 input wire CLK, RST, 3 output reg [3:0] COUNT); 4 5 always @(posedge CLK or posedge RST) begin 6 if (RST) begin 7 COUNT <= 4'h0; 8 end else begin 9 COUNT <= COUNT + 4'h1; 10 end 11 end 12endmodule

テストベンチ

SystemVerilog

1`timescale 1ns / 1ns 2 3module counter_test(); 4 parameter STEP = 10; 5 6 logic CLK; 7 initial begin 8 CLK = 1; 9 forever #(STEP/2) CLK = ~CLK; 10 end 11 12 logic RST; 13 initial begin 14 RST =0; 15 #(2) RST = 1; 16 #(12) RST = 0; 17 end 18 19 logic [3:0] out; 20 counter cnt(.CLK(CLK), .RST(RST), .COUNT(out)); 21 22 initial begin 23 $monitor($time, " count=%b", out); 24 #(STEP*20) $finish; 25 end 26endmodule 27

試したこと

FPGAのPL部分の動作周波数はデフォサイトルトで100MHzということで、超高速でLチカを行いっているのではないかと思いました。

この問題を改善するために調べていたところこちらのサイトを見つけました。

待ち時間を表す入力(CDIV)を入れてあげることで、jupyter bookでIPコアであるAXI GPIOにアクセスして、CDIVの値を書き換えてあげれば、実装時にLチカを確認することができると思いました。

しかし、CDIVを4bitカウンタ回路のプログラムにどのように組み込ませればよいかがわかりません。

ご教授お願いいたします。

補足情報(FW/ツールのバージョンなど)

Windows11

使用したボード:PYNQ-Z1

回答2件

あなたの回答

tips

プレビュー

2022/06/05 01:55